Tranzistoru attīstība: no plakanas līdz CFET, 3D integrācija no jauna definē pusvadītāju progresu

Vairāk nekā pusgadsimtu pusvadītāju rūpniecība pieauga, ievērojot vienu vienkāršu noteikumu: padarīt tranzistorus mazākus.Samazinoši elementu izmēri nodrošināja lielāku veiktspēju, mazāku jaudu un zemākas izmaksas par tranzistoru.Taču šodien šis ceļš ir sasniedzis savu fizisko un ekonomisko robežu.Tīras mērogošanas laikmets ir beidzies, un jauns laikmets strukturālā inovācija un 3D integrācija ir sākusies.

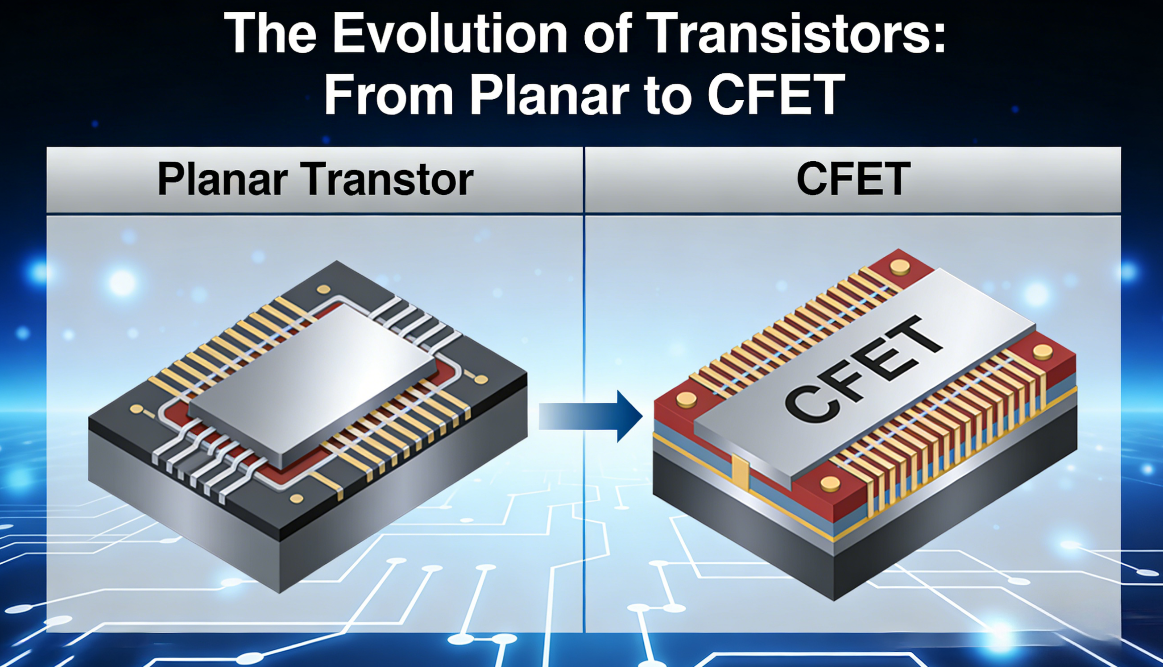

Pats tranzistors piedzīvo pilnīgu arhitektūras revolūciju.No plakanas MOSFET uz FinFET, no GAA nanosheet uz CFET sakraušanu, katrs solis atspoguļo pāreju no saraušanās uz tranzistora pārbūve trīs dimensijās.Tas nav tikai pakāpenisks uzlabojums — tā ir pilnīga mikroshēmu veiktspējas pārdefinēšana.

Četras tranzistoru arhitektūras paaudzes

1. Planārais tranzistors (tradicionālais 2D)

Klasiskā plakana konstrukcija, kur vārti kontrolē kanālu no augšas.Tas dominēja no pirmajām dienām līdz 40 nm un 28 nm.Tā kā izmēri vēl vairāk samazinājās, noplūdes strāva un elektrostatiskā kontrole kļuva par neatrisināmām problēmām.

2. FinFET (3D vārtu vadība)

Kanāls kļūst par vertikālu “spuru”, vārtiem aptinot trīs malas.Tas ievērojami uzlabo elektrostatisko vadību, samazina noplūdi un ļauj samazināt līdz 7 nm, 5 nm un pat 3 nm.FinFET kļuva par mūsdienu augstas veiktspējas mikroshēmu laikmeta pamatu.

3. GAA nanolapa (Gate-All-Around)

Pie 2nm un zemāk FinFET sasniedz savu robežu.GAA aizstāj spuru ar sakrautām horizontālām nanovadām vai loksnēm, kuras pilnībā ieskauj vārti.Tas nodrošina labāku vadību, mazāku jaudu un lielāku piedziņas strāvu.GAA tagad ir galvenā struktūra 2nm klases mikroshēmām TSMC, Samsung un Intel.

4. CFET (papildu FET)

Nākamā robeža: NMOS un PMOS sakraušana vertikāli.CFET apvieno divus tranzistorus vienā vietā, krasi samazinot laukumu un uzlabojot blīvumu.Tas ir tranzistoru mērogošanas galīgais evolūcijas beigas, pirms pārņem patiesa 3D sistēmas integrācija.

Kāpēc mērogošana vienatnē vairs nedarbojas

- Procesa izmaksas pieaug eksponenciāli katrā jaunā mezglā

- Kvantu noplūde un fiziskie ierobežojumi nostiprina robežas

- Starpsavienojumu aizkave un enerģijas patēriņš apsteidz tranzistora ātrumu

- Lielas monolītās skaidas cieš no zemas ražas un augstām izmaksām

Nozare ir sapratusi: veiktspēju vairs nesniedz mazāki tranzistori.Tas nāk no labāki savienojumi, viedāka arhitektūra un vertikālā integrācija.

Jaunā ēra: trīs 3D inovāciju slāņi

Pusvadītāju progresu tagad nosaka trīs 3D dizaina dimensijas:

- 3D tranzistors: FinFET, GAA, CFET – tranzistora uzbūve vertikāli

- 3D ierīču sakraušana: loģikas atmiņa, hibrīda savienošana, SRAM sakraušana

- 3D sistēmu integrācija: Chiplet, 2.5D/3D iepakojums, uz interposer balstīta integrācija

Kopā tie veido 3D × 3D × 3D ēra: tranzistors, ierīce un sistēma kļūst trīsdimensiju.

DTCO: jaunā pamatkompetence

Kad mērogošana beidzas, Dizaina tehnoloģiju kopoptimizācija (DTCO) kļūst kritisks.Tas nozīmē arhitektūras, tranzistora struktūras, metāla maršrutēšanas un iepakojuma kopprojektēšanu jau no paša sākuma.Spēcīgākie uzņēmumi vairs nav tikai procesu vadītāji — tie ir sistēmas līmeņa integratori.

Elektroinstalācijas efektivitāte, strāvas padeve, siltuma dizains un joslas platuma blīvums tagad nosaka produkta reālo veiktspēju.

AI ir galvenais dzinējspēks

AI un augstas veiktspējas skaitļošana prasa vēl nebijušu joslas platumu, energoefektivitāti un blīvumu.Šīs prasības nevar izpildīt, izmantojot tradicionālo mērogošanu.Viņiem ir nepieciešams:

- Īpaši liela joslas platuma atmiņas un skaitļošanas starpsavienojums

- Ekstrēma energoefektivitāte vienā operācijā

- Masīvs paralēlisms un blīva integrācija

AI ir piespiedusi visu nozari atteikties no tīras mērogošanas un pieņemt pilnīgu 3D neviendabīgu integrāciju.

Secinājums: Nākotne nav mazāka, tā ir augstāka

Sarūkošo tranzistoru laikmets izgaist.Pusvadītāju nākotne nav saistīta ar ierīču padarīšanu mazāku, bet gan par sistēmu izveidi augstāks, blīvāks un saprātīgāk savienots.

No Planar līdz FinFET līdz GAA līdz CFET tranzistors ir pabeidzis savu attīstību.Nākamā cīņa tiks izcīnīta 3D integrācija, uzlabots iepakojums un sistēmas līmeņa dizains.Šeit tiks izlemta nākamā pusvadītāju vadības desmitgade.